Amandeep Singh

Senior Research Fellow @ IIT Roorkee

PhD in Electronics and Communication Engineering

Senior Research Fellow @ IIT Roorkee

PhD in Electronics and Communication Engineering

PhD Researcher @ IIT Roorkee

TSMC 65nm

VLSID 2025 & 2026 • Consecutive Wins

Industry-Standard Tools

Prestigious Recognitions

Specializing in In-Memory Computing architectures for energy-efficient AI acceleration. My research bridges the gap between circuit design and system-level AI applications through silicon-proven innovations.

Indian Institute of Technology, Roorkee

Punjab Engineering College, Chandigarh

Guru Gobind Singh College, Kharar

Central Public School, Ghoman

S.G.H.K. Public School, Ghoman

XAC & Multibit MAC Operations

Binary Neural Networks

In-Memory Crypto

128x128 6T-SRAM Array

LED Strip & Persistence of Vision

Analog Design

Low-Power High-Speed

C-DAC Mohali

IEEE ISCAS 2024, Singapore

IEEE iSES 2023, Ahmedabad

IEEE Trans. on Nanotechnology, 2023

IEEE Transactions on Very Large Scale Integration (VLSI) Systems (Communicated)

IEEE Transactions on Circuits and Systems I (Communicated)

Pune, Maharashtra

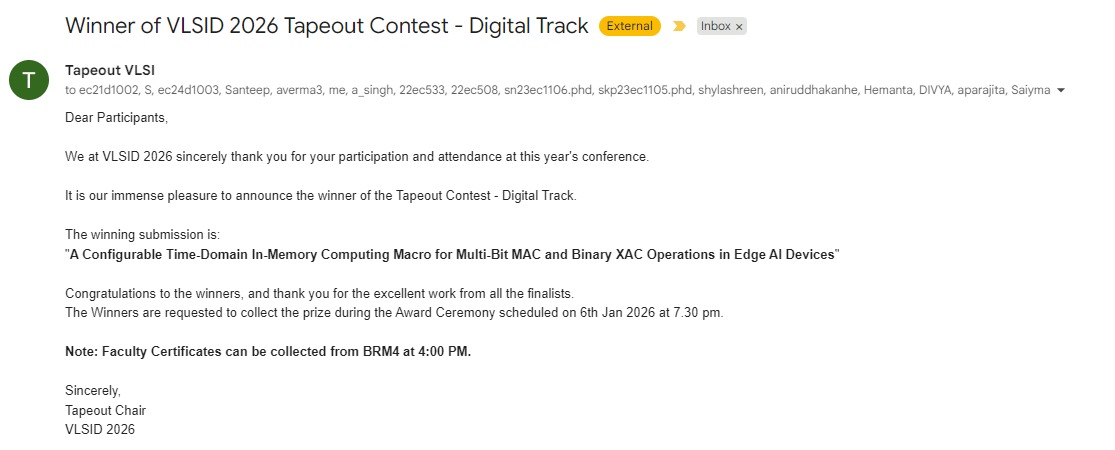

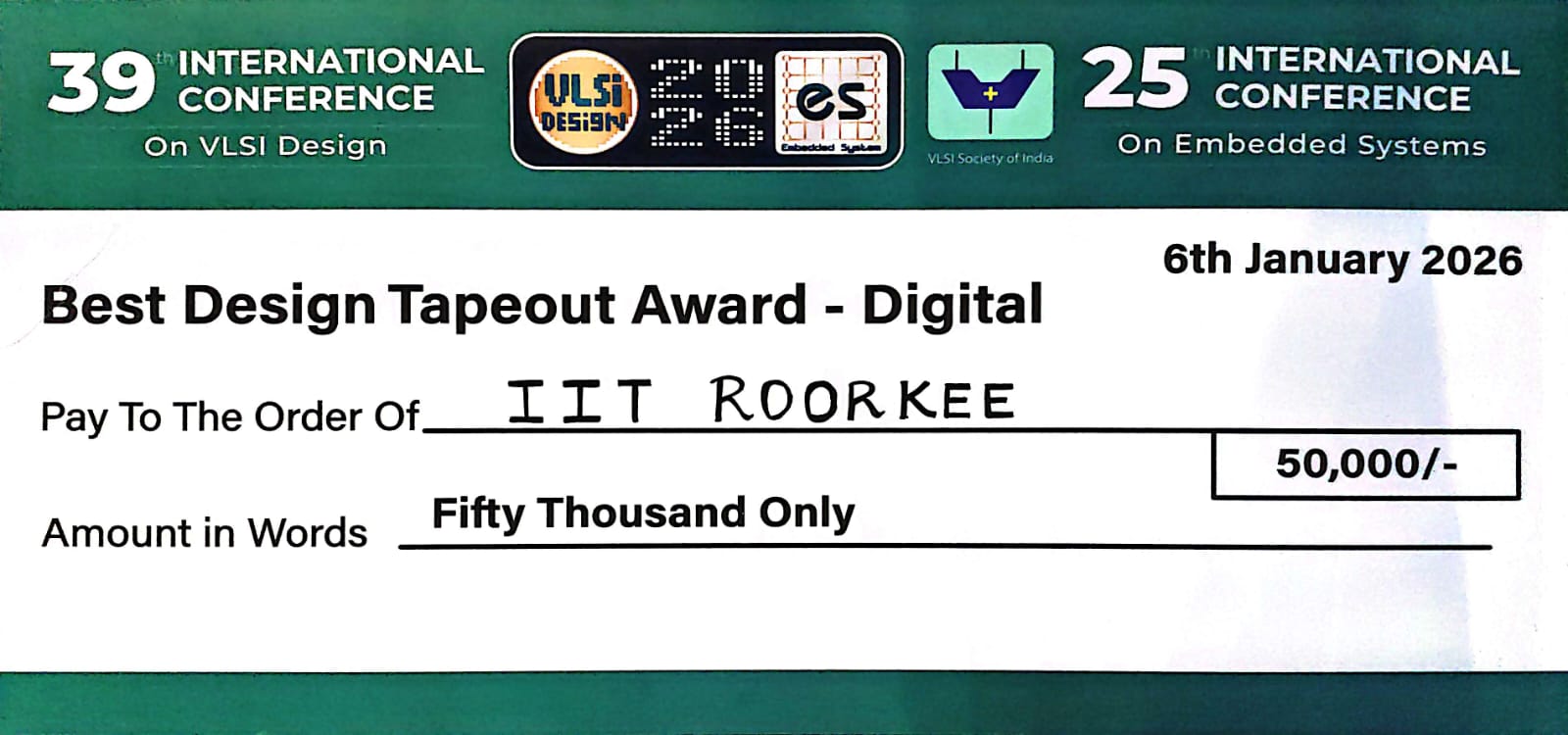

Won the Digital Tape-Out Winner medal at the 39th VLSI & 25th Embedded Conference. Research titled: "A Configurable Time-Domain In-Memory Computing Macro for Multi-Bit MAC and Binary XAC Operations in Edge AI Devices". Received a prize cheque of ₹50,000.

Pune, Maharashtra

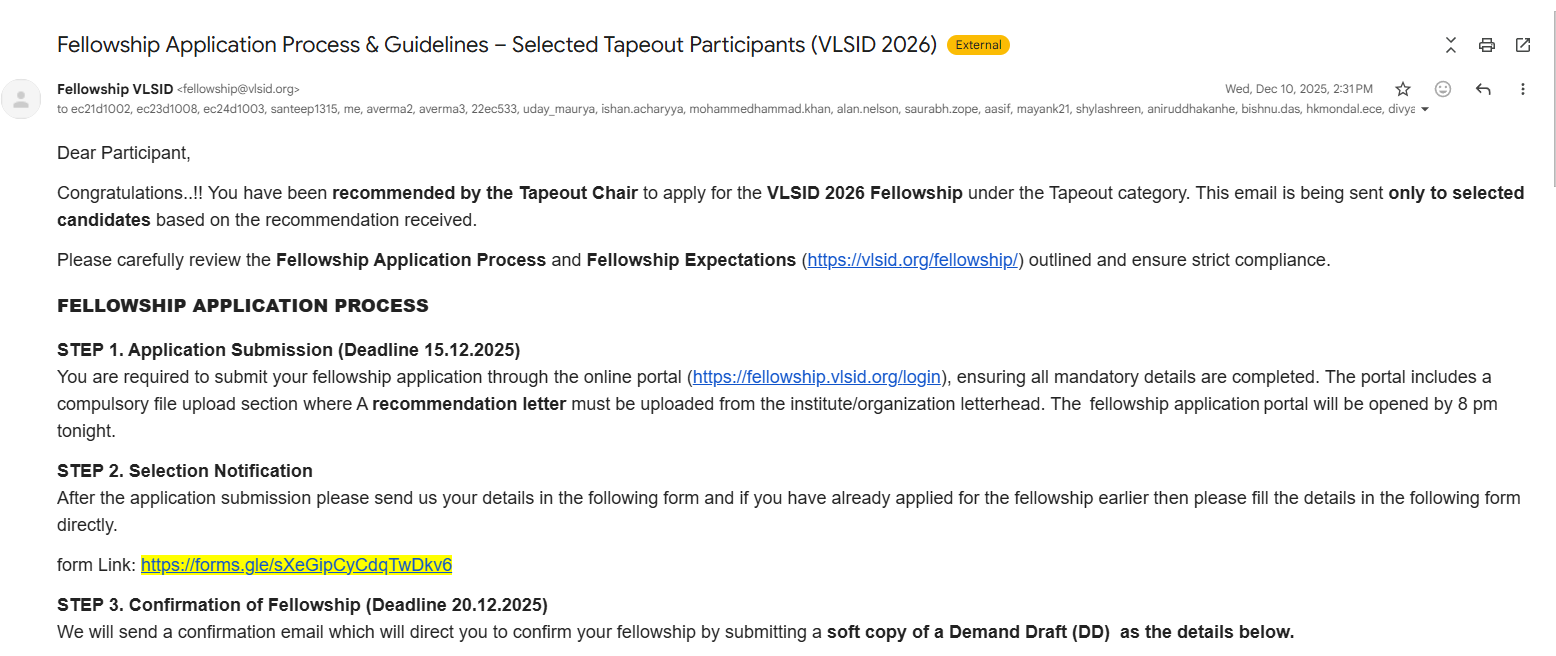

Selected for the prestigious VLSID 2026 Fellowship under the Tapeout category based on strong recommendations. Fellowship application process with deadline 15.12.2025.

Pune, Maharashtra

Presented the winning research titled "A Configurable Time-Domain In-Memory Computing Macro for Multi-Bit MAC and Binary XAC Operations in Edge AI Devices" at the Award Ceremony of the 39th VLSI Design Conference.

Prize Cheque ₹50,000

Received the Best Design Tapeout Award – Digital, including a prize cheque of ₹50,000 at VLSID 2026.

Bengaluru, Karnataka

Honored with the Best Digital IC Tapeout Award at the 38th International Conference on VLSI Design as part of the IIT Roorkee team. Team: Saragada Prasanna Kumar, Anu Verma, Anshul Verma, Aranya Gupta, Amandeep Singh, Mentor: Prof. Bishnu Prasad Das.

Bengaluru, Karnataka

Received the official certificate for the Best Digital IC Tapeout Award, recognizing the team's outstanding contribution in digital IC design at VLSID 2025. Team: Saragada Prasanna Kumar, Anu Verma, Anshul Verma, Aranya Gupta, Amandeep Singh, Mentor: Prof. Bishnu Prasad Das.

Bengaluru, Karnataka

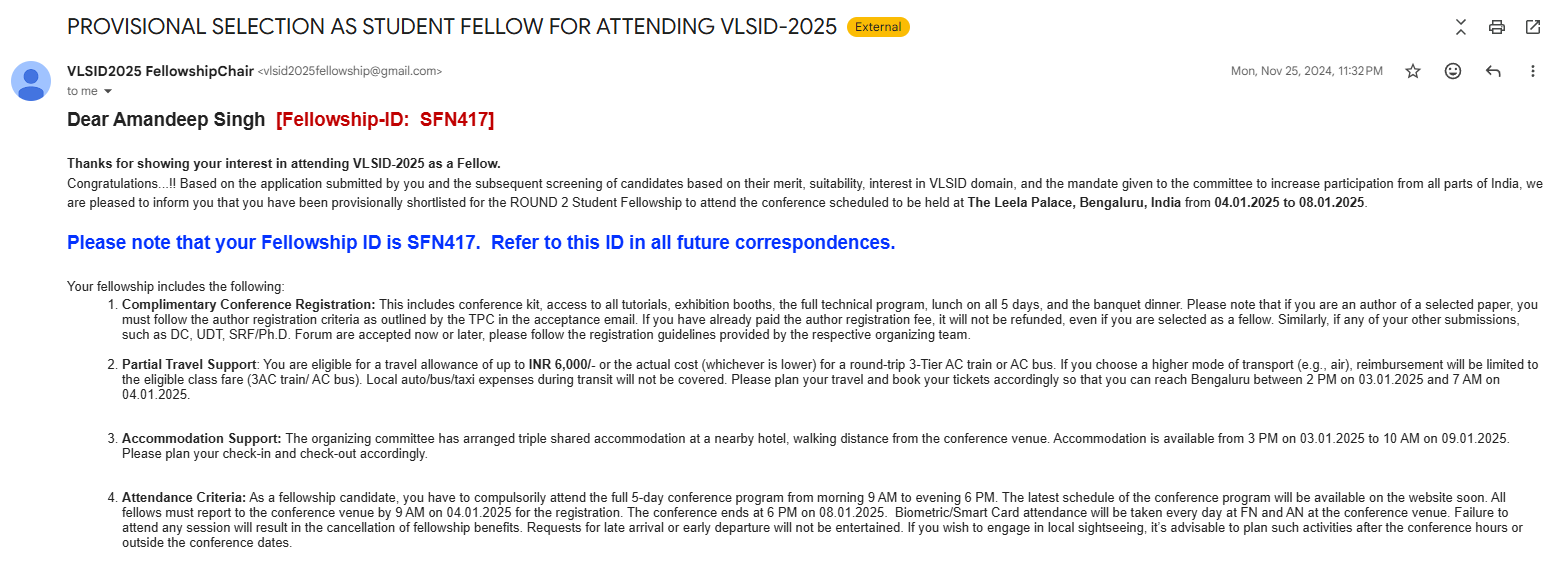

Selected as a Student Fellow (SFN417) with full conference registration, accommodation, and travel support. Fellowship includes complimentary registration, travel allowance up to INR 6,000, and triple shared accommodation.

ISCAS 2024, Singapore

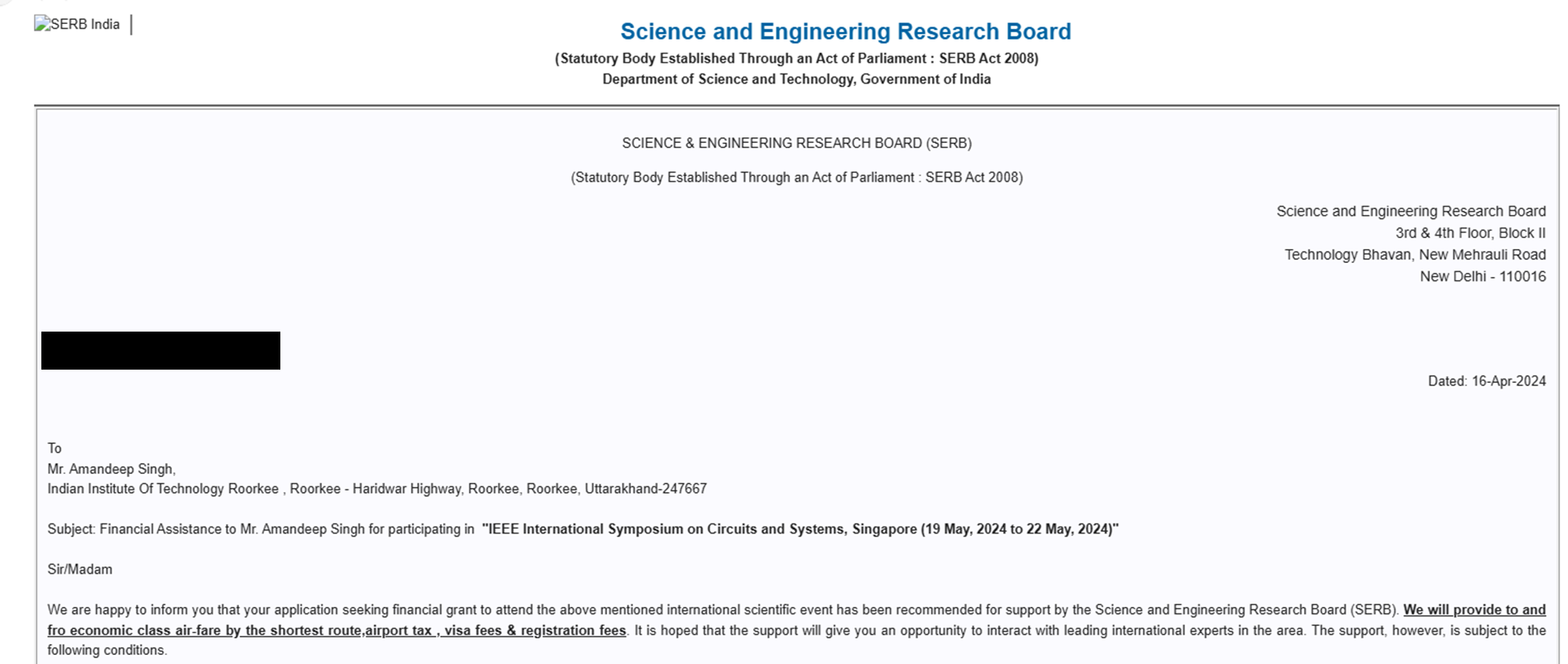

Awarded by the Science and Engineering Research Board (SERB), Department of Science and Technology, Government of India to attend and present at the IEEE International Symposium on Circuits and Systems (ISCAS) 2024. Includes to and from economic class air-fare, airport tax, visa fees, and registration fees.

ISCAS 2024, Singapore

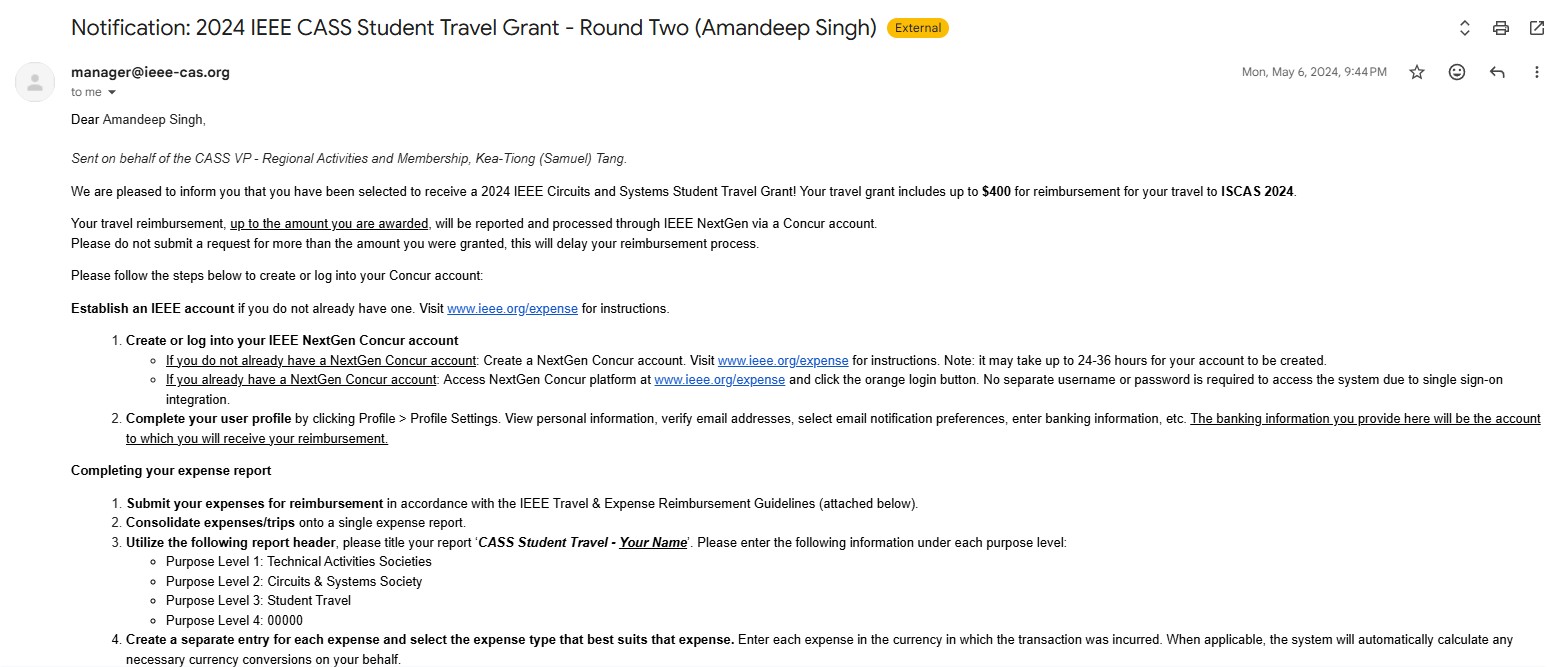

Recipient of the 2024 IEEE Circuits and Systems Society (CASS) Student Travel Grant of up to $400 for reimbursement of travel expenses to attend ISCAS 2024.

Kolkata, West Bengal

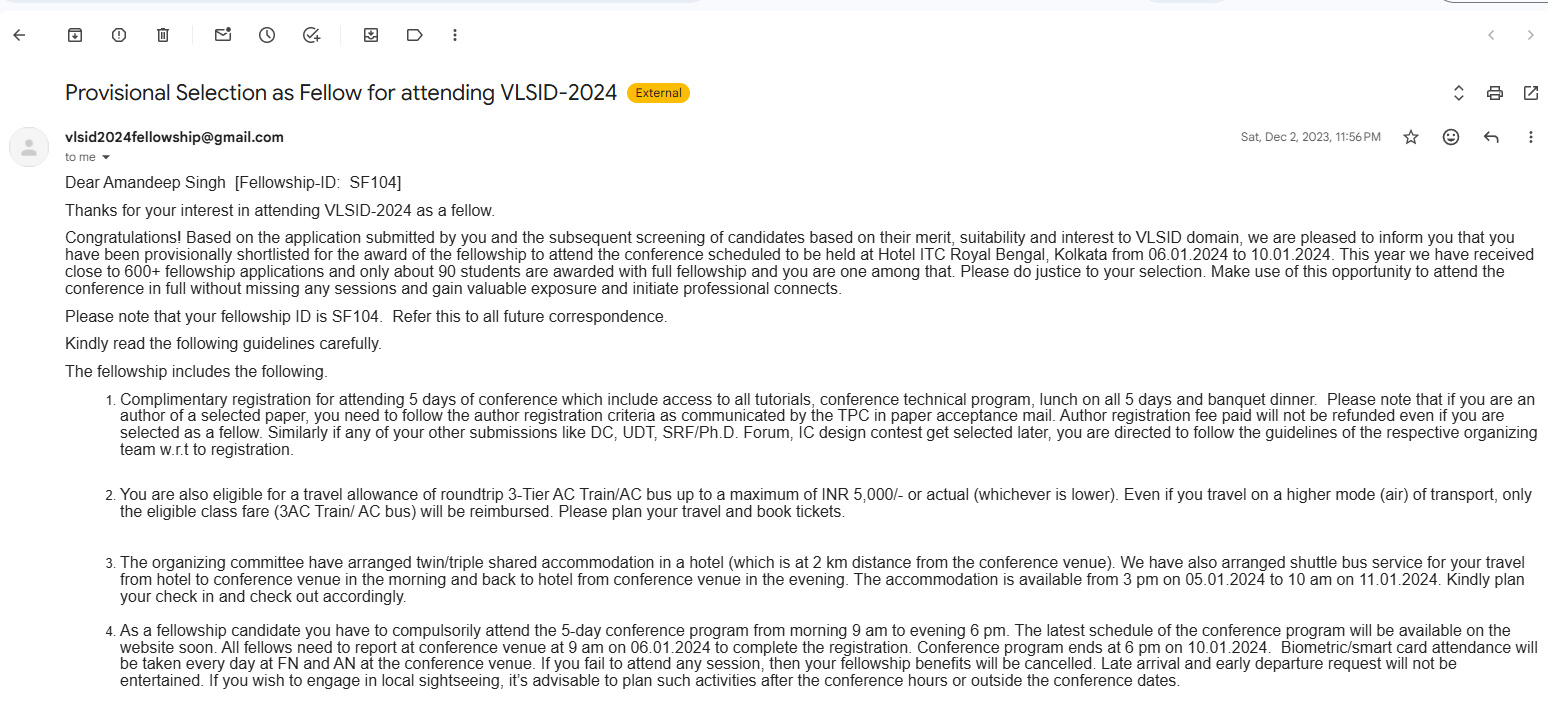

Selected as a Fellow (SF104) from over 600 applicants nationwide for the 37th International Conference on VLSI Design. Only about 90 students were awarded with full fellowship including complimentary registration, travel allowance up to INR 5,000, and twin/triple shared accommodation.

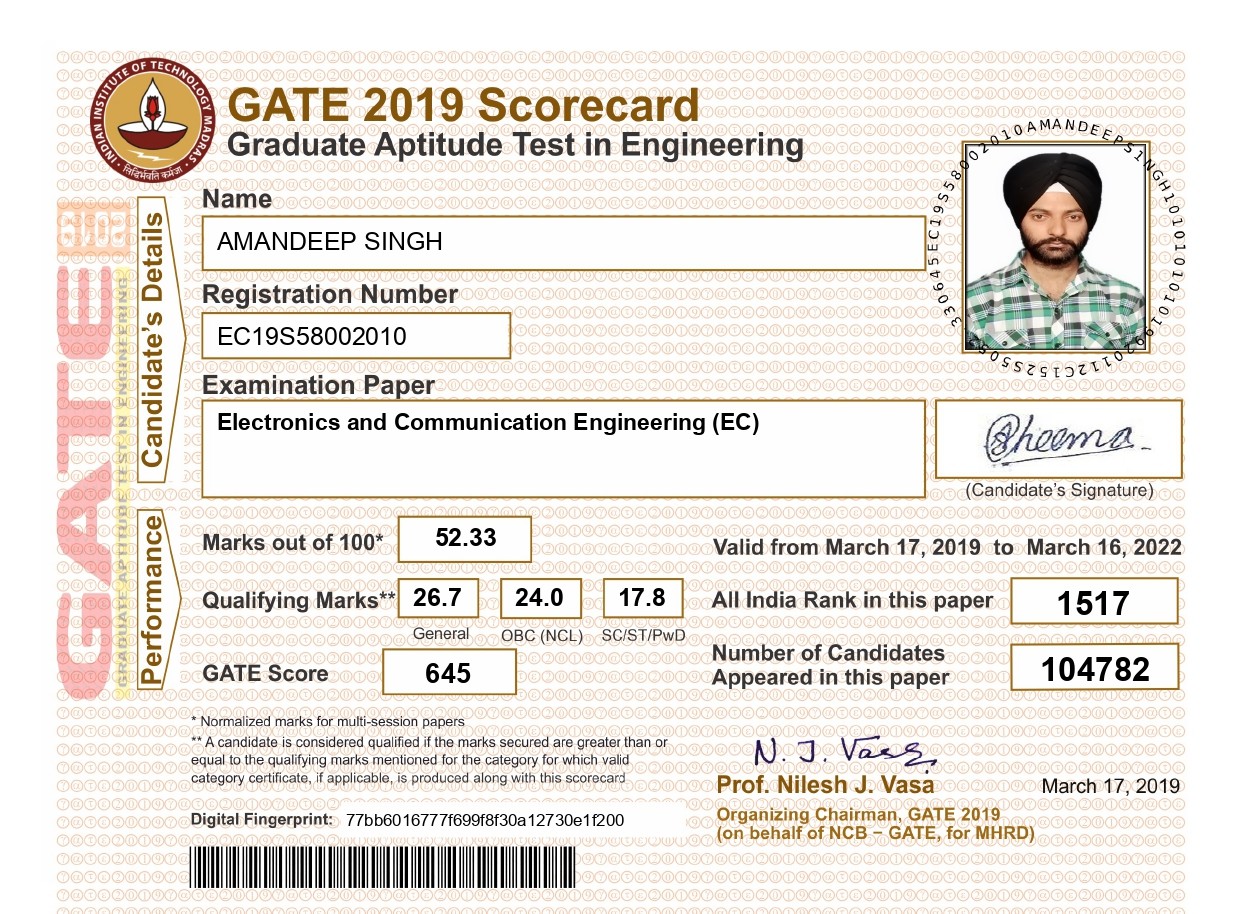

AIR 1517 | Score 645

Secured All India Rank 1517 in Electronics and Communication Engineering with a score of 645. Marks: 52.33 out of 100. Appeared among 104,782 candidates.

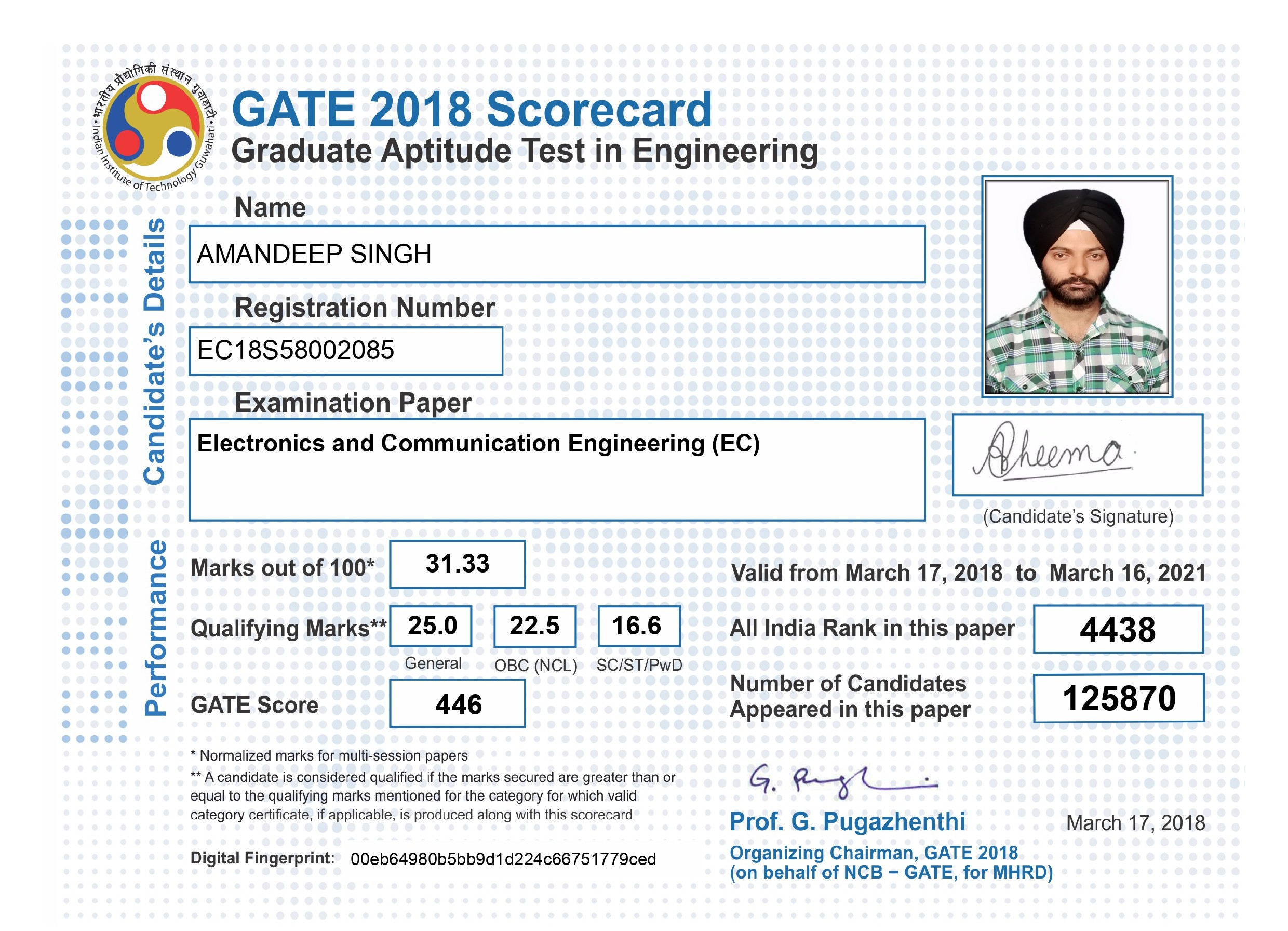

AIR 4438 | Score 446

Secured All India Rank 4438 in Electronics and Communication Engineering with a score of 446. Marks: 31.33 out of 100. Appeared among 125,870 candidates.

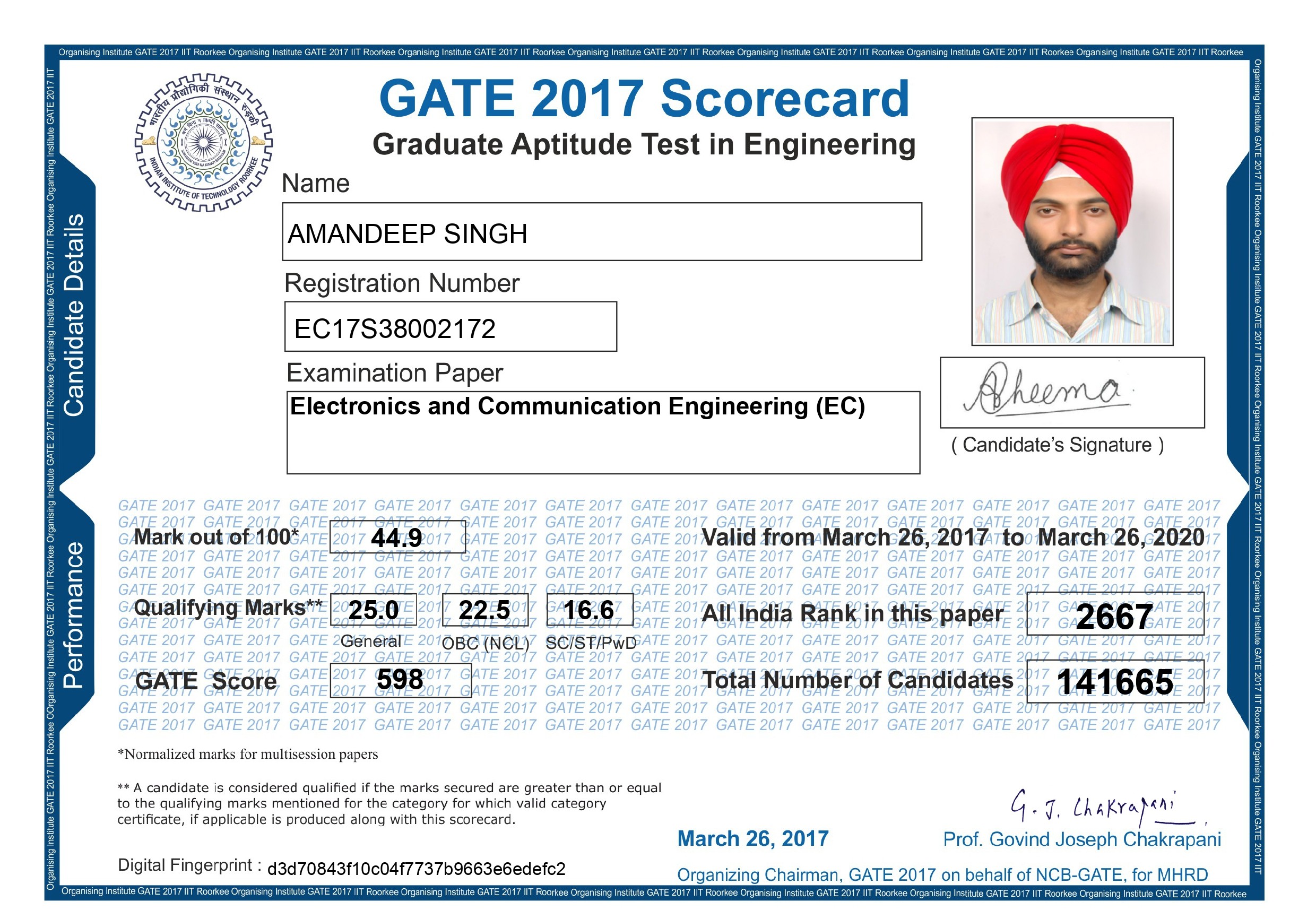

AIR 2667 | Score 598

Secured All India Rank 2667 in Electronics and Communication Engineering with a score of 598. Marks: 25.0 out of 100. Appeared among 125,870 candidates.

All chips fabricated in TSMC 65nm • Funded by SERB

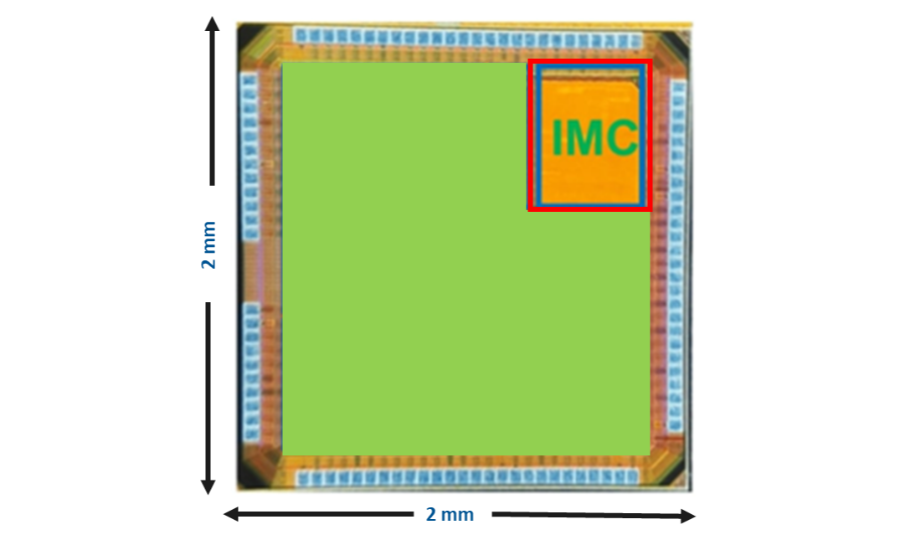

TSMC 65nm | 2mm x 2mm

A robust and PVT-insensitive Time-Domain In-Memory Compute architecture using an SRAM array, designed to adaptively control PVT variations.

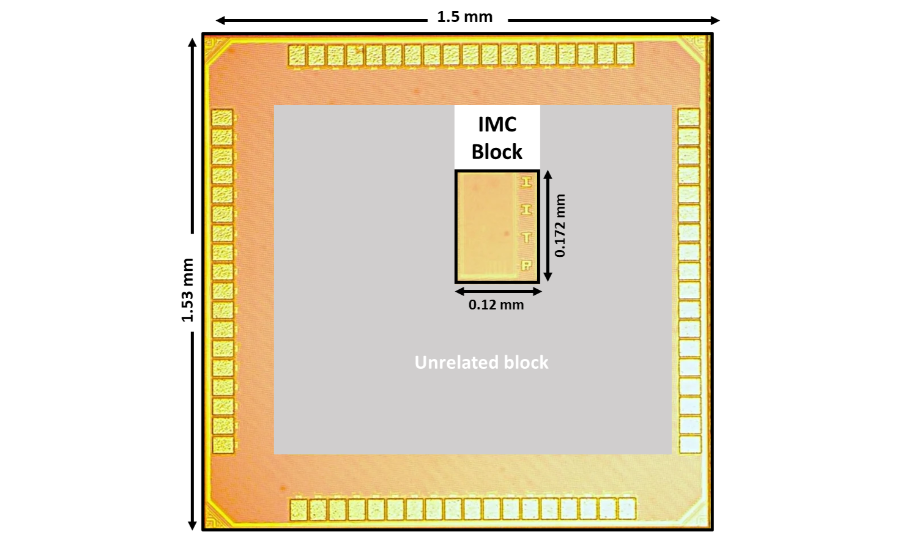

TSMC 65nm | 1.53mm x 1.5mm

Utilizes a voltage-controlled delay cell (VCDC) integrated with an SRAM array to perform XAC and MAC operations for AI applications.

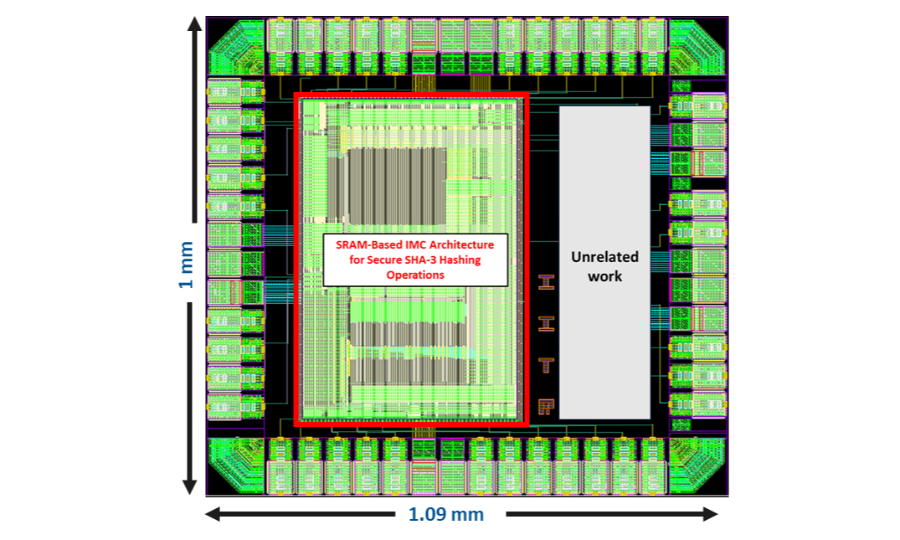

TSMC 65nm | 1mm x 1.09mm

An in-memory architecture to accelerate Secure Hash Algorithm-3 (SHA-3) computation, implementing 5-input XOR and fused XOR-Rotation operations.

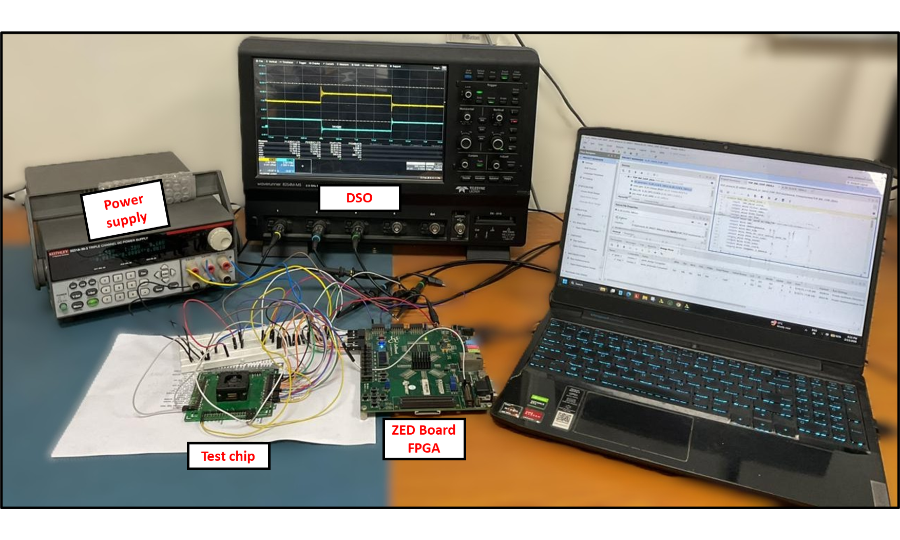

IC Testing Laboratory, IIT Roorkee

Test chip validation setup for functional verification of fabricated designs using industry-standard testing equipment.

Pune • 39th VLSI Design Conference

Honored with the Best Digital IC Tapeout Award at VLSID 2026, marking a consecutive second-time achievement after winning the same award at VLSID 2025.

Pune • 39th VLSI Design Conference

Documented during the Award Ceremony of VLSID 2026, receiving the Best Digital IC Tapeout Award.

Pune

During the VLSID 2026 Conference at Pune, commemorating participation and achievements at the event.

with Rajat Kumar Singh, Founder & CEO

Featured in an interview with Rajat Kumar Singh, Founder & CEO of VLSI FOR ALL, discussing critical EDA tools and methodologies required for successful tapeout and testing in VLSI design.

Pune

Presenting measured chip results and silicon validation of the designed IMC architecture.

IEEE International Symposium

Presenting "PVT-Insensitive Time-Domain-based In-Memory Computation with Improved Linearity for Binary Neural Networks."

IIT Roorkee

The lab where the tapeouts were designed and tested, under the supervision of Professor Bishnu Prasad Das.

Fellow (SFO1041)

Certificate of Participation for attending the 39th VLSI Design Conference.

Tapeout Selection

Certificate for the presented tapeout research at VLSID 2026.

Singapore

Certificate of attendance and presentation at the IEEE International Symposium on Circuits and Systems.

Kolkata

Attended as a VLSID 2024 Fellow at the 37th International Conference.

Ahmedabad

Presented paper on "Area-Efficient In-Memory Computation" at the 9th International Symposium on Smart Electronics Systems.

Virtual Event

Fellowship Certificate for contribution at the 34th International Conference on VLSI Design.

Mohali

Completed a 6-week industrial training on "Design and Development of Embedded Based Quiz Game."

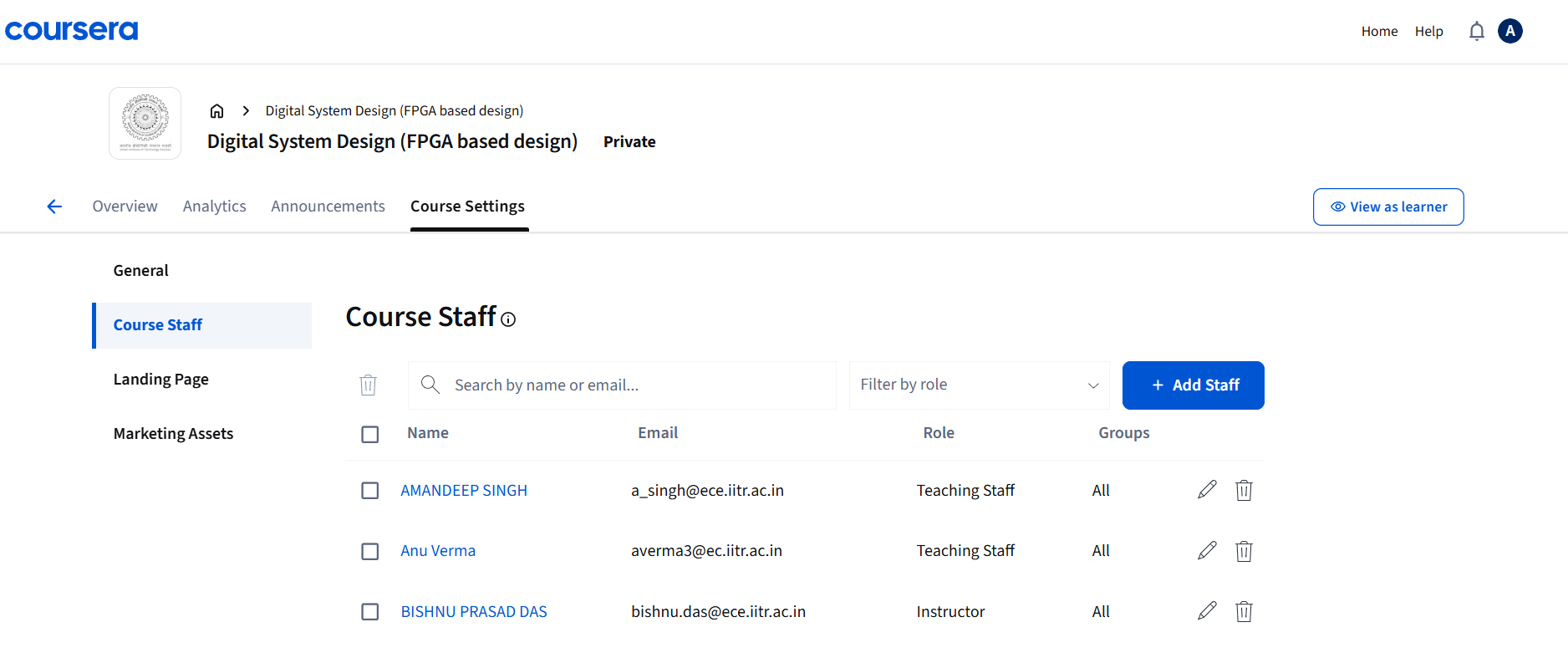

Digital System Design

Recognized for contributions to online learning initiatives with Prof. Bishnu Prasad Das.

VLSI Physical Design

Certificate of Appreciation for transcribing course materials for an NPTEL course by IIT Roorkee.

+91 9501286656

Dr. Bishnu Prasad Das

Professor, Department of ECE

IIT Roorkee

bishnu.das@ece.iitr.ac.in

+91-1332-28479